Physical design interview questions

- Below are the sequence of questions asked for a physical design engineer.

In which field are you interested?

- Answer to this question depends on your interest, expertise and to the requirement for which you have been interviewed.

- Well..the candidate gave answer: Low power design

Can you talk about low power techniques?

How low power and latest 90nm/65nm technologies are related?

Do you know about input vector controlled method of leakage reduction?

- Leakage current of a gate is dependant on its inputs also. Hence find the set of inputs which gives least leakage. By applyig this minimum leakage vector to a circuit it is possible to decrease the leakage current of the circuit when it is in the standby mode. This method is known as input vector controlled method of leakage reduction.

How can you reduce dynamic power?

- -Reduce switching activity by designing good RTL

- -Clock gating

- -Architectural improvements

- -Reduce supply voltage

- -Use multiple voltage domains-Multi vdd

What are the vectors of dynamic power?

How will you do power planning?

If you have both IR drop and congestion how will you fix it?

- -Spread macros

- -Spread standard cells

- -Increase strap width

- -Increase number of straps

- -Use proper blockage

Is increasing power line width and providing more number of straps are the only solution to IR drop?

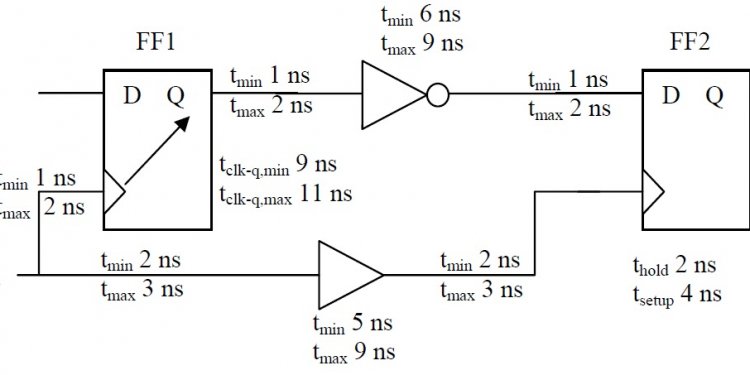

In a reg to reg path if you have setup problem where will you insert buffer-near to launching flop or capture flop? Why?

- (buffers are inserted for fixing fanout voilations and hence they reduce setup voilation; otherwise we try to fix setup voilation with the sizing of cells; now just assume that you must insert buffer !)

- Because there may be other paths passing through or originating from the flop nearer to lauch flop. Hence buffer insertion may affect other paths also. It may improve all those paths or degarde. If all those paths have voilation then you may insert buffer nearer to launch flop provided it improves slack.

What is the most challenging job in P&R flow?

- -It may be power planning- because you found more IR drop

- -It may be low power target-because you had more dynamic and leakage power

- -It may be macro placement-because it had more connection with standard cells or macros

- -It may be CTS-because you needed to handle multiple clocks and clock domain crossings

- -It may be timing-because sizing cells in ECO flow is not meeting timing

- -It may be library preparation-because you found some inconsistancy in libraries.

- -It may be DRC-because you faced thousands of voilations

How will you synthesize clock tree?

- -Single clock-normal synthesis and optimization

- -Multiple clocks-Synthesis each clock seperately

- -Multiple clocks with domain crossing-Synthesis each clock seperately and balance the skew

How many clocks were there in this project?

- -It is specific to your project

- -More the clocks more challenging !

How did you handle all those clocks?

- -Multiple clocks->synthesize seperately->balance the skew->optimize the clock tree

Are they come from seperate external resources or PLL?

- -If it is from seperate clock sources (i.e.asynchronous; from different pads or pins) then balancing skew between these clock sources becomes challenging.

- -If it is from PLL (i.e.synchronous) then skew balancing is comparatively easy.

Why buffers are used in clock tree?

- To balance skew (i.e. flop to flop delay)

What is cross talk?

- Switching of the signal in one net can interfere neigbouring net due to cross coupling capacitance.This affect is known as cros talk. Cross talk may lead setup or hold voilation.

How can you avoid cross talk?

- -Double spacing=>more spacing=>less capacitance=>less cross talk

- -Multiple vias=>less resistance=>less RC delay

- -Shielding=> constant cross coupling capacitance =>known value of crosstalk

- -Buffer insertion=>boost the victim strength

How shielding avoids crosstalk problem? What exactly happens there?

- -High frequency noise (or glitch)is coupled to VSS (or VDD) since shilded layers are connected to either VDD or VSS.

- Coupling capacitance remains constant with VDD or VSS.

How spacing helps in reducing crosstalk noise?

- width is more=>more spacing between two conductors=>cross coupling capacitance is less=>less cross talk

Why double spacing and multiple vias are used related to clock?

- Why clock?- because it is the one signal which chages it state regularly and more compared to any other signal. If any other signal switches fast then also we can use double space.

- Double spacing=>width is more=>capacitance is less=>less cross talk